#### **Taxonomy of Dynamic Power Saving Techniques in Fixed Broadband Networks**

#### Ralph Schlenk<sup>(1)</sup>, Christoph Lange<sup>(2)</sup>, Heiko Lehmann<sup>(2)</sup>, Ron Vleugel<sup>(1)</sup>

<sup>(1)</sup> Alcatel-Lucent Deutschland AG, Thurn-und-Taxis-Straße 10, 90411 Nürnberg, Germany <sup>(2)</sup> Deutsche Telekom AG, Telekom Innovation Laboratories, Winterfeldtstraße 21, 10781 Berlin, Germany

**Introduction & Motivation**

**Dynamic aspects of load-adaptive networking**

**Network reconfiguration time characteristics**

**Measurements and results**

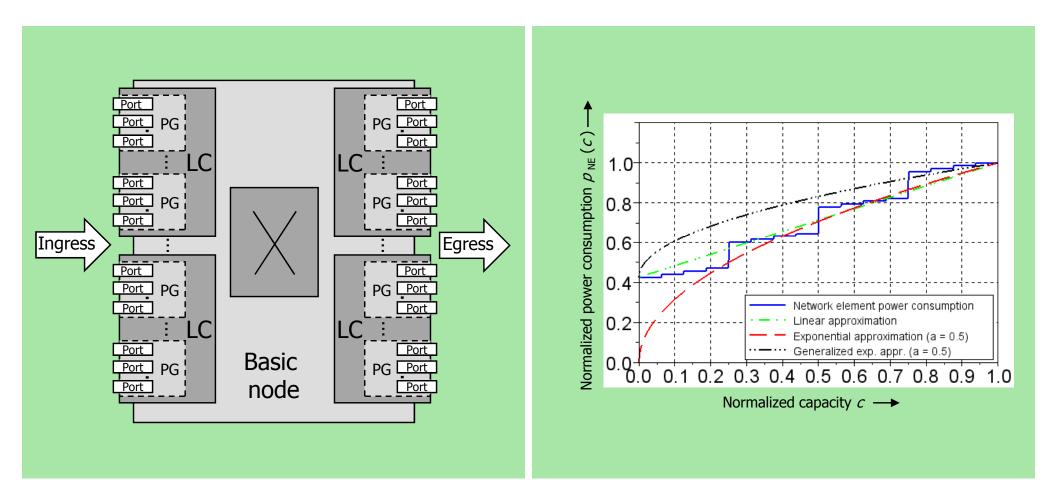

# **INTRODUCTION** GENERIC NETWORK ELEMENT MODEL

Lange, C.; Schlenk, R.; Lehmann, H.: Network Element Characteristics for Traffic Load Adaptive Network Operation. In: *13. ITG-Fachtagung Photonische Netze*. Leipzig, 07.–08. Mai 2012.

**Introduction & Motivation**

**Dynamic aspects of load-adaptive networking**

**Network reconfiguration time characteristics**

**Measurements and results**

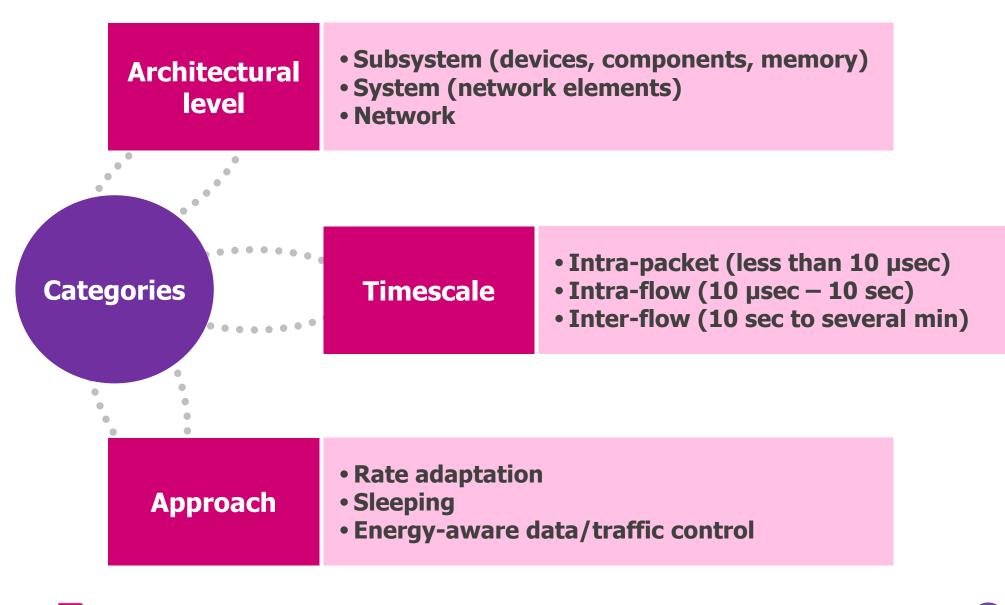

# **CLASSIFICATION**

5

······ Alcatel · Lucent

## **POWER-SAVE TECHNIQUES TAXONOMY AND ACTIVATION TIMES**

| Approach                                    | Subsystem                                         |                |           | System                                   |         | Network                     |                              |         |

|---------------------------------------------|---------------------------------------------------|----------------|-----------|------------------------------------------|---------|-----------------------------|------------------------------|---------|

| Rate<br>Adaptation                          | Dynamic<br>voltage<br>and<br>frequency<br>scaling | CPU P-states   | 10-100 µs | DSL L2 mode                              | <1 s    |                             |                              |         |

|                                             |                                                   | Memory<br>DVFS | <100 µs   | Ethernet RPS                             | 20 ms   |                             |                              |         |

| Sleeping                                    | CPU C-states (C1, C2)                             |                | 10-100 ns | DSL L3 mode                              | <3 s    |                             |                              |         |

|                                             | CPU C-states (C3)                                 |                | 50 µs     | PON dozing                               | 1 µs    |                             |                              |         |

|                                             | DRAM power-down                                   |                | <10 ns    | PON fast sleeping                        | <200 µs |                             |                              |         |

|                                             | DRAM self refresh                                 |                | <1 µs     | PON deep sleeping                        | -       |                             |                              |         |

|                                             | CMOS clock gating                                 |                | 10 ns     | EEE low-power idle                       | 1-25 ms |                             |                              |         |

|                                             | CMOS clock and power gating                       |                | 5 µs      |                                          |         |                             |                              |         |

|                                             | FPGA suspend techniques                           |                | <100 µs   |                                          |         |                             |                              |         |

| Energy-<br>aware<br>data/traffic<br>control | CPU idle core "hotplug"                           |                | 5 ms      | Ethernet background<br>traffic buffering | 5-20 µs | Energy-<br>aware<br>routing | Interface<br>shutdown        | >10 s   |

|                                             | Power-aware virtual<br>memory                     |                | <1 µs     |                                          |         |                             | Line card<br>shutdown        | > 30 s  |

|                                             |                                                   |                |           |                                          |         |                             | Chassis<br>shutdown          | minutes |

|                                             |                                                   |                |           |                                          |         |                             | Protocol<br>conver-<br>gence | n/a     |

**Introduction & Motivation**

**Dynamic aspects of load-adaptive networking**

**Network reconfiguration time characteristics**

**Measurements and results**

# **RECONFIGURATION TIME SERIAL SWITCHING OF COMPONENTS**

# Analytical formulation

Activation times (switching on)

$$T_{_{\rm NE\,ON}}^{\rm S}(C_{\rm in},C_{\rm fi}) = T_{_{\rm C_{ON}}} + \sum_{i=1}^{n_{_{\rm LC_{ON}}}} T_{_{\rm LC_{ON}i}} + \sum_{j=1}^{n_{_{\rm PG_{ON}}}} T_{_{\rm PG_{ON}j}} + \sum_{l=1}^{n_{_{\rm PON}}} T_{_{\rm PON}j}$$

De-activation times (switching off)

$$T_{_{\text{NE OFF}}}^{\text{S}}(C_{\text{in}}, C_{\text{fi}}) = T_{C_{\text{OFF}}} + \sum_{i=1}^{n_{\text{LC}_{\text{OFF}}}} T_{\text{LC}_{\text{OFF}i}} + \sum_{j=1}^{n_{\text{PG}_{\text{OFF}j}}} T_{\text{PG}_{\text{OFF}j}} + \sum_{l=1}^{n_{\text{POFF}j}} T_{P_{\text{OFF}j}}$$

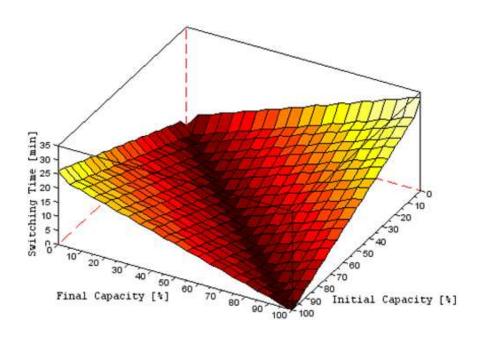

#### **Exemplary** result

#### The capacity differences determine the switching times.

# **RECONFIGURATION TIME PARALLEL SWITCHING OF COMPONENTS**

# Analytical formulation

Activation times (switching on)

$T_{_{\text{NEON}}}^{P}(C_{_{\text{in}}}, C_{_{\text{fi}}}) = T_{_{\text{C}_{\text{ON}}}} + T_{_{\text{LC}_{\text{ON}}}} + T_{_{\text{PG}_{\text{ON}}}} + T_{_{\text{P}_{\text{ON}}}} + \dots$ Parameter accounts

for additional organization effort

De-activation times (switching off)

$$T_{\text{NEOFF}}^{P}(C_{\text{in}}, C_{\text{fi}}) = T_{C_{\text{OFF}}} + T_{\text{LC}_{\text{OFF}}} + T_{\text{PG}_{\text{OFF}}} + T_{P_{\text{OFF}}} + \dots$$

$$\dots + \Delta T_{\text{OFF}}(n_{\text{LC}} + n_{\text{PG}} + n_{\text{P}})$$

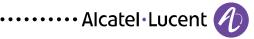

#### Exemplary result

Capacity differences and  $\Delta T$  determine the switching times.

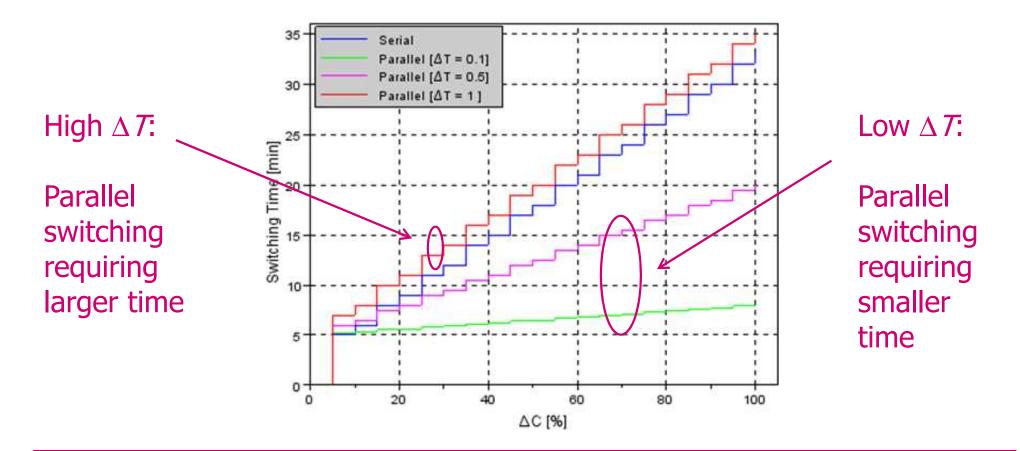

## **RECONFIGURATION TIME COMPARISON OF SWITCHING STRATEGIES**

Additional processing organization time  $\Delta T$  is critical.

•• Alcatel • Lucent 🥢

# OUTLINE

**Introduction & Motivation**

**Dynamic aspects of load-adaptive networking**

**Network reconfiguration time characteristics**

**Measurements and results**

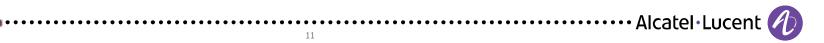

## **IMPROVING ACTIVATION TIMES DESIGN PRINCIPLES**

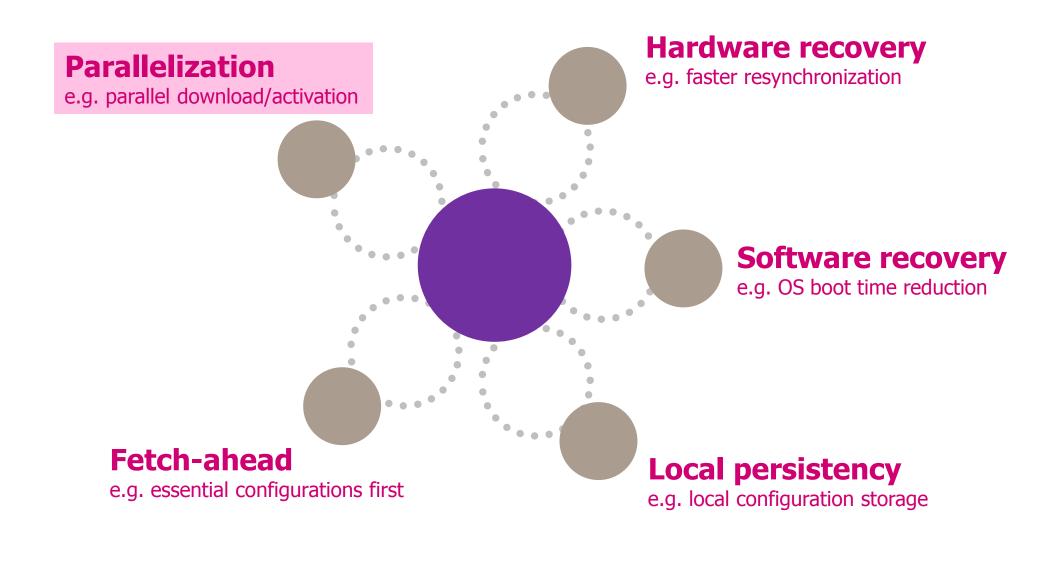

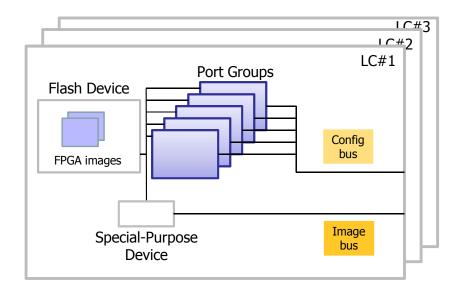

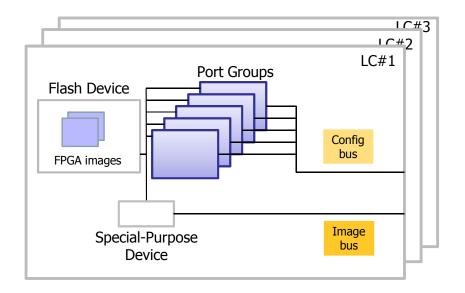

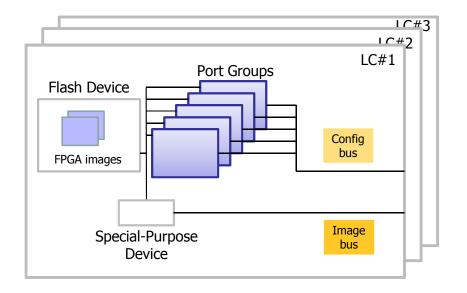

# **IMPROVING ACTIVATION TIMES EXAMPLE: LINE CARD ACTIVATION (1)**

- Line card (LC) with several port groups (PG)

- Two hardware busses (image bus, config bus)

- Two software processes

- Equipment management (EM)

- Transmission management (TM)

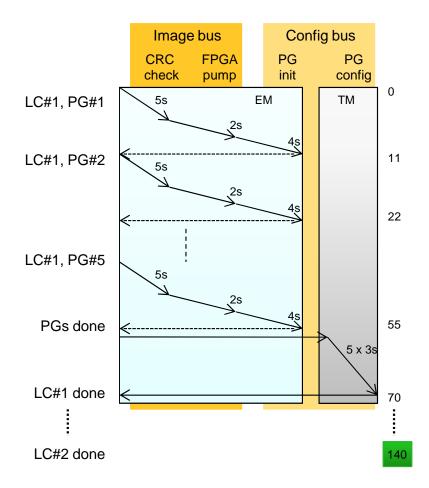

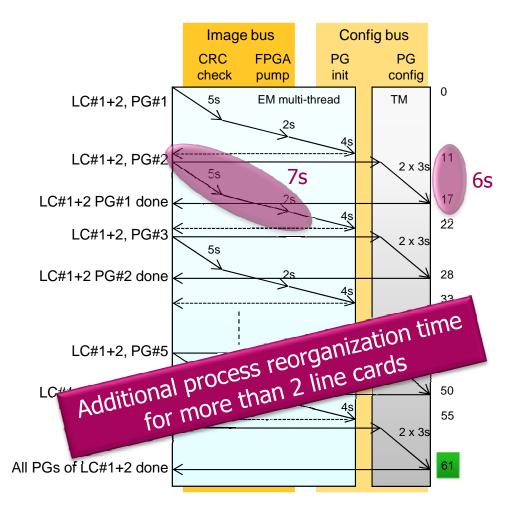

# **IMPROVING ACTIVATION TIMES EXAMPLE: LINE CARD ACTIVATION (2)**

- Line card (LC) with several port groups (PG)

- Two hardware busses (image bus, config bus)

- Two software processes

- Equipment management (EM)

- Transmission management (TM)

······ Alcatel Lucent

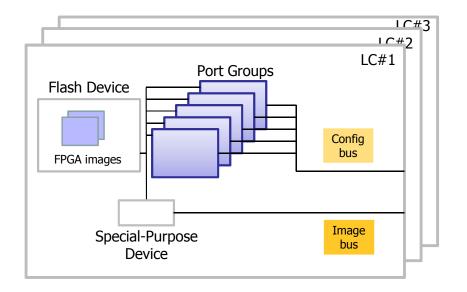

# **IMPROVING ACTIVATION TIMES EXAMPLE: LINE CARD ACTIVATION (3)**

- Line card (LC) with several port groups (PG)

- Two hardware busses (image bus, config bus)

- Two software processes

- Equipment management (EM)

- Transmission management (TM)

······ Alcatel·Lucent 🥢

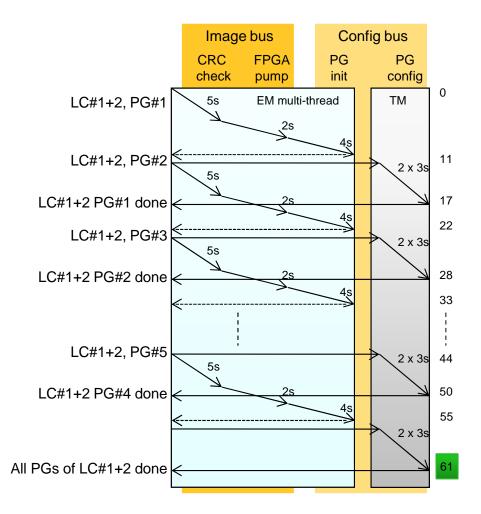

# **IMPROVING ACTIVATION TIMES EXAMPLE: LINE CARD ACTIVATION (4)**

- Line card (LC) with several port groups (PG)

- Two hardware busses (image bus, config bus)

- Two software processes

- Equipment management (EM)

- Transmission management (TM)

······ Alcatel Lucent 🥢

# OUTLINE

**Introduction & Motivation**

**Dynamic aspects of load-adaptive networking**

**Network reconfiguration time characteristics**

**Measurements and results**

# CONCLUSION

| Taxonomy     | <ul> <li>Categorization of power management techniques according to their temporal properties</li> <li>Network-level technologies most critical with respect to network performance degradation</li> <li>→ Coordination required, e.g. by an energy-aware control plane</li> </ul> |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Model        | <ul> <li>Modeling of network resource activation processes</li> <li>→ Extension of the network element power-vs-capacity model</li> <li>Evaluation of serial and parallel switching strategies</li> </ul>                                                                          |  |  |  |

| Optimization | <ul> <li>Analysis of a current-generation OTN network element</li> <li>Serial line card activation process optimized (from 140 sec to 61 sec for two line cards)</li> <li>Challenges observed when software process split does not match hardware partitioning</li> </ul>          |  |  |  |

. .

**1**